# TI 製 DSP スタータキット(DSK)対応

高速・高精度拡張インターフェース

DSK6713IF/AIO2 同時変換 500ksps A/D2ch,D/A2ch DSK6416IF/AIO2 同時変換 500ksps A/D2ch,D/A2ch

ハードウエア テクニカル・マニュアル

HEG 有限会社 平塚エンジニアリング

#### 1. 高速・高精度拡張インターフェースの概要

TMS320C6713/6416T対応高速・高精度拡張インターフェースは、TI製スタータキット(以下DSKと称します)に接続して、高精度な多チャンネルディジタル信号処理技術の研究や高機能なDSPアプリケーションの開発など幅広くご利用いただけます。

#### 2. 対応 DSK と製品型名

| DSK 型名 | TMS320C6713DSK |

|--------|----------------|

| 当社型名   | DSK6713IF/AIO2 |

| A/D 変換 | 2 チャンネル        |

| D/A 変換 | 2 チャンネル        |

| DSK 型名 | TMS320C6416DSK |

| 当社型名   | DSK6416IF/AIO2 |

| A/D 変換 | 2 チャンネル        |

| D/A 変換 | 2 チャンネル        |

#### 3. 特長

A/D から D/A までの時間遅延を最小に設計,高速応答のディジタル信号処理を行うことが可能。 16 ビット A/D コンバータを各チャンネルに搭載のため全チャンネル同位相(同時変換)でのデータ収集が可能。

16 ビット D/A コンバータを各チャンネルに搭載のため全チャンネル同位相(同時変換)でのデータ出力が可能。

#### 最高サンプリングクロックが 500kHz のため高速処理が可能。

入力レベルは,±10∨または±1∨対応、ディップスイッチでチャンネルごとに選択可能。

(ユーザーのご希望によりユニポーラ仕様にするこのも可能)

出力レベルは,±10Vまたは±1V対応、ディップスイッチでチャンネルごとに選択可能。

(ユーザーのご希望によりユニポーラ仕様にするこのも可能)

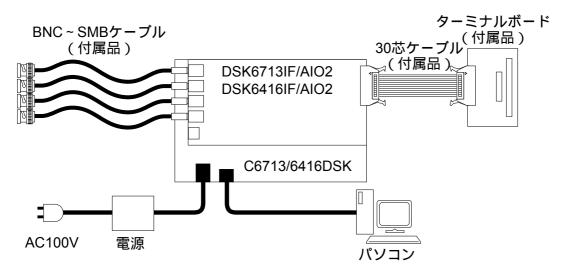

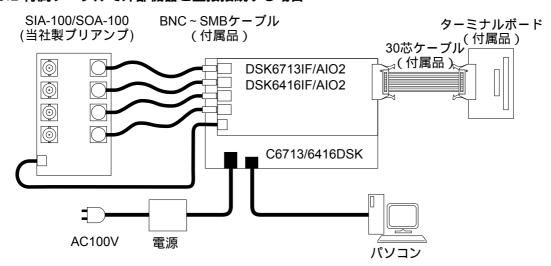

入出力コネクタには同軸コネクタ(SMB)を使用。

サンプリングクロックに同期して A/D,D/A 変換がされるためチャンネル間の位相ずれがない。 ディジタル入出力回路の装備により、外部ディジタル回路の拡張が容易。

各機能の設定は、設定スイッチもしくは内部設定レジスタから行える。

デバックに便利な、ユーザースイッチと LED を搭載。

電源は DSK から供給されるため外部電源は不要。

外部との接続に便利な入出ケーブル、ターミナルボードが付属しており余分な準備が不要。

入出力のサンプルプログラムが付属されるため開発期間の短縮が図られます。

(ポーリング・割り込み・DMA など多数用意)

拡張ボード、サンプルプログラムなど全て当社で開発した製品のためユーザーサポートは万全。などの特長を持ち、DSKによる本格的な信号処理の実現ができます。

#### 4. 用途

ディジタルサーボ ・ ディジタル信号処理 ・ 適応信号処理 ・スペクトル分析・生体信号処理など

## 5. 構成図

#### 5.1 付属ケーブルで外部機器と直接接続する場合

#### 5.2 付属ケーブルで外部機器と直接接続する場合

当社の製品 SIA-100 又は SOA-100 は DSKxxxxIF/AIO2 と外部機器とのレベルマッチングを目的に開発された製品で入力 2CH、出力 2CH が用意されており、入出力信号のレベルマッチングを行うことが出来ます。(ユーザーの希望仕様に合わせ出荷可能)

## 6.主な仕様

## 6.1 A/D **変換**

| 入力チャンネル数    | 2 チャンネル                         |

|-------------|---------------------------------|

| 入力形式        | 全チャンネル同時変換                      |

| 入力信号        | チャンネル毎に AC, DC 結合の選択が可能         |

| 入力電圧        | ±1V または ±10V(チャンネル毎に設定可能) 1     |

| 調整用         | LEVEL, GAIN, OFFSET チャンネルごとに調整可 |

|             | 能                               |

| A/D 変換の主要仕様 | 最高サンプリング周波数 500KHz 16 ビット       |

| サンプリングクロック  | 内部サンプリングクロック, A/D 用外部クロック端      |

|             | 子,                              |

|             | DSPTIMER0 出力, DSPTIMER1 出力      |

|             | (プログラムによるポーリングも可能)              |

| 内部サンプリングクロッ | 1KHz ~ 500KHz (64 段階選択可)        |

| ク周波数        |                                 |

| 変換方式        | 逐次比較方式                          |

| 入力インピーダンス   | 100K                            |

| 入力フィルタ      | チャンネル毎に1次 CR フィルタ (有無切替え可)      |

## 6.2 D/A **変換**

| 出力チャンネル数    | 2 チャンネル                     |

|-------------|-----------------------------|

| 出力形式        | 全チャンネル同時変換                  |

| 出力信号        | DC 結合                       |

| 出力電圧        | ±1V または ±10V(チャンネル毎に設定可能) 2 |

| 調整用         | GAIN, OFFSET チャンネルごとに調整可能   |

| D/A 変換の主要仕様 | 最高サンプリング周波数 500KHz 16 ビット   |

| サンプリングクロック  | 内部サンプリングクロック, D/A 用外部クロック端  |

|             | 子,                          |

|             | DSPTIMER0 出力, DSPTIMER1 出力  |

|             | (プログラムによるポーリングも可能)          |

| 内部サンプリングクロッ | 1KHz ~ 500KHz ( 64 段階選択可 )  |

| ク周波数        |                             |

| 負荷インピーダンス   | 1K 以上                       |

## 6.3 ディジタル入出力

| 外部入力  | 8 ビット TTL レベル正論理 10k でプルアップ |

|-------|-----------------------------|

| 外部出力  | 12 ビット TTL レベル正論理 8mA 以下    |

| ユーザ入力 | 4 回路のディップスイッチ               |

| ユーザ出力 | 4 回路のモニタ LED                |

## 6.4 その他の入出力

| 外部サンプリング入力 | 1 回路 TTL レベル正論理 | 10k でプルアップ |

|------------|-----------------|------------|

| 部サンプリング出力  | 1 回路 TTL レベル正論理 | 8mA 以下     |

1.ユーザーのご希望によりユニポーラ仕様に変更が可能です。

2.ユーザーのご希望によりユニポーラ仕様に変更が可能です。

## 6.5 **物理仕樣他**

| 電源     | +5V DSK から給電              |

|--------|---------------------------|

| 外形寸法   | 240 (W) ×86 (D) ×25 (H)   |

| 接続コネクタ | ・アナログ入出力:SMB 同軸コネクタ       |

|        | ・デジタル入出力:30 芯フラットケーブルコネクタ |

|        | ( 2.54mm ピッチ )            |

|        |                           |

| 付属品    | ・ターミナルボード                 |

|        | ・BNC~SMB ケーブル 0.5m        |

|        | ・30 芯フラットケーブル 0.5m        |

|        | ・サンプルプログラム CD-ROM         |

|        | ・ジャンパーソケット、ねじなど小物部品       |

## 6.6 拡張性

本ボードの半田面と部品面には拡張コネクタが搭載されており、最大 8 台まで増設が可能です。 なお、各ボードのアドレス認識はボード上のマイアドレスディップスイッチで行います。

## 7.レジスタ

本 IF ボードへのアクセスは、レジスタとディップスイッチを用いて行います。 レジスタ詳細は次のとおりです。

## 7.1 レジスタマップ一覧

| アドレス(h)     | 名 称                      | 説 明                                                  |

|-------------|--------------------------|------------------------------------------------------|

| BASE + 0000 | Ch0 A/D 変換データレジスタ        | Ch0 の A/D 変換結果が格納されます。                               |

| BASE + 0004 | Ch1 A/D 変換データレジスタ        | Ch1 の A/D 変換結果が格納されます。                               |

| BASE + 0040 | Ch0 D/A 変換データレジスタ        | Ch0 の D/A 変換データをストアします。                              |

| BASE + 0044 | Ch1 D/A 変換データレジスタ        | Ch1 の D/A 変換データをストアします。                              |

| BASE + 0080 | A/D 変換スタート/完了フラグレ<br>ジスタ | プログラムからポーリングで A/D 変換を開始する場合に使用します。<br>変換完了も取得できます。   |

| BASE + 0084 | D/A 変換スタート/完了フラグレ<br>ジスタ | プログラムからポーリングで D/A 変換を開始する場合に使用します。<br>変換完了も取得できます。   |

| BASE + 00C0 | ユーザ LED レジスタ             | DSKxxxxIF/AIO2 上の LED の点灯/消灯を制御します。デバッグなどに使用すると便利です。 |

| BASE + 00C4 | ユーザスイッチレジスタ              | DSK6713IF/AIO2 上のユーザーSW の値を取得します。デバッグなどに使用すると便利です。   |

| BASE + 0100 | ディジタル OUT1 レジスタ          | 外部出力端子の制御レジスタです。                                     |

| BASE + 0104 | ディジタル OUT2 レジスタ          | 外部出力端子の制御レジスタです。                                     |

| BASE + 0140 | ディジタル IN レジスタ            | 外部入力端子の取得レジスタです。                                     |

| BASE + 0144 | (予 約)                    |                                                      |

| BASE + 0180 | 設定レジスタ 1                 | DSKxxxxlF/AlO2 の設定レジスタです。                            |

| BASE + 0184 | 設定レジスタ 2                 | DSKxxxxlF/AlO2 の設定レジスタです。                            |

| BASE + 01C0 | 製品 No レジスタ               | 製品識別番号レジスタです。0x3302 が書き込まれています                       |

| BASE + 01C4 | トグルビットレジスタ               | 1msec の間隔でビットが反転します。本ボードの起動状態を確認することができます。           |

BASE アドレスは基板上のディップスイッチ MY\_ADDRESS 及び BOARD\_NO により 0xA000 0000(h) ~ 0 x A038 0038 ( h ) の範囲で使用できます。

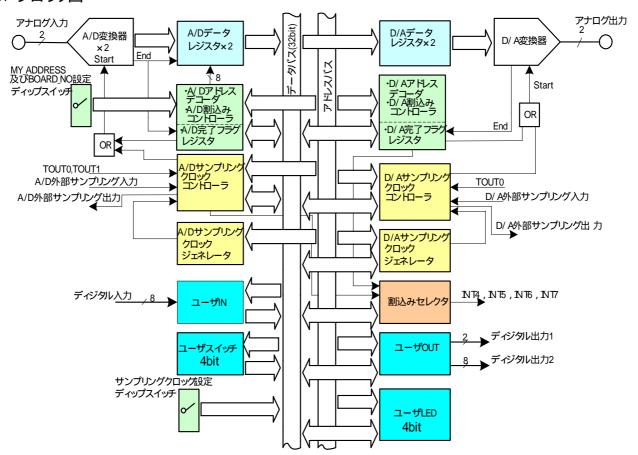

## 8. ブロック図

- 9.各レジスタ及び入出力ポートの内容

- 9.1A/D 変換データレジスタ

- (1). A/D 変換完了で全チャンネル同時に本レジスタに格納され、格納された結果は次のサンプルクロックでの A/D 変換完了まで保持されます。

- (2). 取得される A/D 変換データは 16 ビットで、レジスタの下位 16 ビットに格納され、上位 16 ビットは取得した値に準じた符号が格納 (符号拡張) されます。

よって32ビットでのリードを行うことができます。

#### 9.2 D/A 変換データレジスタ

- (1). D/A 変換を行うデータを格納するレジスタです。変換データは全チャンネル同時にディジタル アナログ変換されます。また変換されたアナログ出力は次の D/A 変換までのあいだ保持されます。

- (2). D/A 変換データは 32 ビット、もしくは下位 16 ビットにライトしてください。SignBit には DATA Bit15 に従いストアされ符号拡張が行われます。(Bit31~16 へのライトデータは無視されます。) D/A 変換は DATA Bit15~0 をもとに行われます。なお本レジスタはリードも可能です。

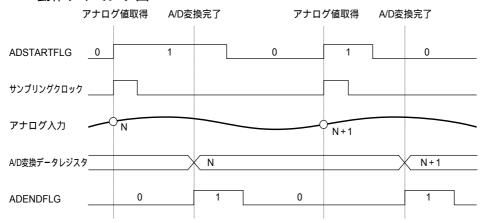

#### 9.3 A/D **変換開始 トリガ/完了 フラグレジスタ**

- (1).プログラムから A/D 変換開始トリガ"1"をセットします。

- (2).A/D 変換完了で A/D 変換データレジスタに変換データは保持され,変換完了フラグ"1"が本レジスタにセットされます。連続して A/D を行う場合その都度上記をおこなってください。

- 9.4 D/A **変換開始 トリガ/完了フラグレジスタ**

- (1). D/A 変換データレジスタ変換データを書き込み D/A 変換開始トリガ"1"をセットします。

- (2).D/A 変換完了で変換完了フラグ"1"がセットされ,ます。

連続して D/A を行う場合その都度上記をおこなってください。

9.5 設定レジスタ 1

A/D **及び** D/A **のためのサンプリングクロックコントローラでクロックソースの選択** 及びサンプリングクロック周波数の設定用レジスタです。

- (1).A/D のクロックソースは下記の通りとし設定レジスタ 1 により設定します。

- A/D 変換サンプリングクロックジェネレータ

- A/D 変換外部サンプリングクロック入力端子

- DSP Timer0 出力 (TOUT0)

- DSP Timer1 出力 (TOUT1)

- (2).D/A のクロックソースは下記の通りとし設定レジスタ 1 により設定します。

- A/D 変換サンプリングクロックコントローラ

- D/A 変換外部クロック端子

- D/A 変換クロックジェネレータ

- DSP Timer1 出力

(3).A/D 及び D/A のサンプリングクロックの周波数は下記とする。

kHz

| OFF  | 4.00  | 12.50 | 40.00 | 100.00 | 192.00 | 300.00 | 400.00 |

|------|-------|-------|-------|--------|--------|--------|--------|

| 1.00 | 5.00  | 15.00 | 44.11 | 110.09 | 200.00 | 311.68 | 406.77 |

| 1.10 | 6.00  | 16.00 | 48.00 | 120.00 | 210.52 | 320.00 | 421.05 |

| 1.20 | 7.50  | 18.00 | 50.00 | 125.00 | 220.18 | 338.02 | 444.44 |

| 1.50 | 8.00  | 20.00 | 60.00 | 140.35 | 240.00 | 347.82 | 452.83 |

| 2.00 | 10.00 | 25.00 | 75.00 | 150.00 | 250.00 | 358.95 | 461.53 |

| 2.50 | 10.99 | 30.00 | 80.00 | 160.00 | 260.86 | 375.00 | 480.00 |

| 3.00 | 12.00 | 32.00 | 96.00 | 180.45 | 279.06 | 380.95 | 500.00 |

#### 記 1.A/D 及び D/A の変換開始 トリガ/完了フラグレジスタによる場合 OFF にします。

記 2.上記以外のサンプリングクロック周波数を使用の場合、外部サンプリングクロックによる方法で任意の周波数を入力してください。

## 9.6 設定レジスタ 2

A/D および D/A に対する・割込可・不可・割込みポートの選択をおこなうための設定レジスタです。

- (1).A/D または D/A 変換完了時・割込み可・不可の設定をおこないます。

- (2).A/D または D/A 変換完了時の DSK に対する割り込みポートの選択で INT4,INT5,INT6 IN7 の内いずれかを選択します。

- 9.7 ディジタル出力ポート 1.2

| 名 称     | ビット数  | 出力レベル  | 出力電流 loL |

|---------|-------|--------|----------|

| ユーザ出力 1 | 8 bit | TTL 5V | 8mA 以下   |

| ユーザ出力 2 | 2 bit | TTL 5V | 8mA 以下   |

## 9.8 ディジタル入力ポート

ビット数:8bit

入力レベル: TTL 5V

入力プルアップ抵抗:10k

#### 9.9 ユーザ LED ポート

ボード上に4個のLEDを搭載し点灯/消灯を制御します。デバッグなどに使用すると便利です。

#### 9.10 ユーザスイッチポート

ボード上に4個のユーザーSWを搭載し値を取得します。デバッグなどに使用すると便利です。

## 10.動作説明

- 10.1 A/D データの取得には・ポーリングによる取得・割込みによる取得・DMA による取得

- の3種類があり内容は下記の通りです。

#### ポーリングによる取得

プログラムからフラグを立てることによりデータの取得を行います。

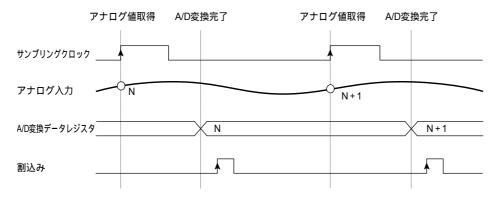

## 動作タイミング図

## 割込みによる取得

「A/D 変換サンプリングクロック」に同期して A/D 変換が行われ、変換終了後割込みが発生します。割込みルーチン内でデータの取得を行います。

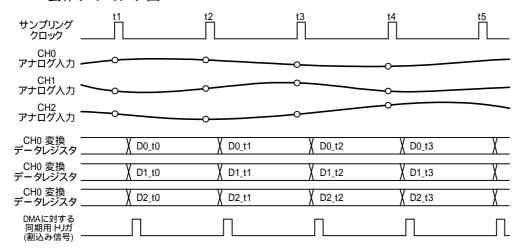

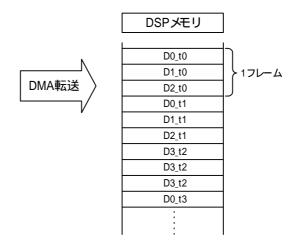

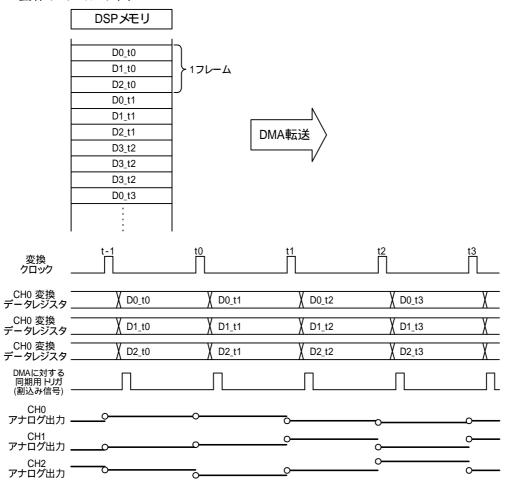

## DMA による取得

転送先バッファアドレス、転送データ数などをあらかじめ指定しておき、DMA によりバックグラウンドでデータの取得を行います。

DMA 動作概要

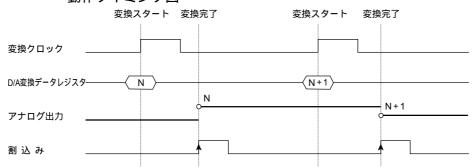

11.2 D/A 変換には・**ポーリングによる変換・割込みによる変換・**DMA **による変換の** 3 **種**

## 類があり内容は下記の通りです。

ポーリングによる変換

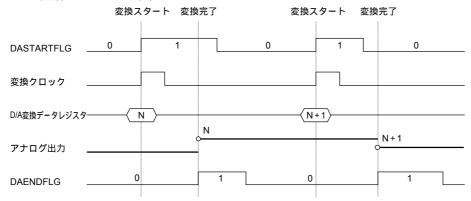

プログラムからフラグを立てることによりデータの変換を行います。

#### 動作タイミング図

#### 割込みによる変換

「D/A 変換用変換クロック」に同期して D/A 変換が行われ、変換終了後割込みが発生します。割込みルーチン内で変換データのストアを行います。

## DMA による変換

転送元バッファアドレス、転送データ数などをあらかじめ指定しておき、DMA によりバックグラウンドにてデータの変換を行います。

DMA 動作概要

## 12.サンプルプログラム構成

| thru1 | AD DAのスルー                                |

|-------|------------------------------------------|

|       | ・ ポーリングによる取得(プログラムによる AD, DA のスタート)      |

|       | ・ ディップスイッチによる設定                          |

|       | ・ 外部割込み(INT4~7)は使用しません。                  |

|       | Timer0(DSP ペリフェラル)を使用してサンプリングクロックを発生させてい |

|       | ます。                                      |

| thru2 | AD DAのスルー                                |

|       | ・ 内部発生サンプリングクロックによる AD データの取得            |

|       | ・ ディップスイッチによる設定                          |

|       | 外部割込み(INT4)を使用                           |

| thru3 | AD DAのスルー                                |

|       | ・ 内部発生サンプリングクロックによる AD データの取得            |

|       | ・ DSKIF(HEG)への設定は「設定レジスタ」から行う            |

|       | ・ 外部割込み(INT4)を使用                         |

|       |                                          |

| dma1a | DMA を使った AD データの取得                       |

|       | ・ DMA を使って 1 チャンネル AD データの取得             |

|       | ・ 取得したデータを CCS グラフ機能にて表示                 |

|       |                                          |

| dma1b | DMA を使った AD データの取得                       |

|       | ・ DMA を使って 2 チャンネル AD データの取得             |

|       | ・ 取得したデータを CCS グラフ機能にて表示                 |

|       |                                          |

| dma2a | DMA を使った DA データの出力                       |

|       | ・ DMA を使った 1 チャンネル DA データの出力             |

|       |                                          |

| dma2b |                                          |

|       | ・ DMA を使った 2 チャンネル DA データの出力             |

|       |                                          |

| dma3a |                                          |

|       | ・ DMA を使った 1 チャンネル AD データの取得             |

|       | ・ DMA を使った 1 チャンネル DA データの出力             |

|       | ・ ピンポンバッファを使用                            |

|       |                                          |

| dma3b | DMA を使った AD DA のスルー出力                    |

|       | ・ DMA を使った 2 チャンネル AD データの取得             |

|       | ・ DMA を使った 2 チャンネル DA データの出力             |

|       | ピンポンバッファを使用                              |

|       |                                          |

Memo:

2007年2月2日 制定

# **HEG** 有限会社 平塚エンジニアリング

〒243-0023 神奈川県厚木市戸田 1073-12 TEL:046-220-0460 FAX:046-220-0461 http://www.heg.co.jp

E-mail: contact@heg.co.jp